Universal Interface Board は外部接続コネクタ、内部拡張コネクタ(汎用、クロック供給)の3種類4個のコネクタをもっています。

これまで、研究開発上必要になって、汎用のオプション回路をつくってきましたので紹介します。

4CH 14bit 300ksps ADユニット

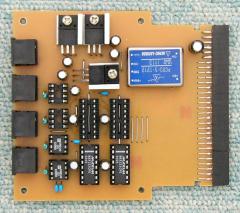

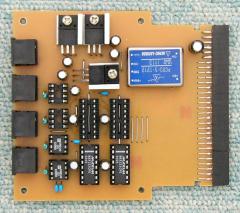

UnivIFのアナログフロントエンドとして開発したAD変換ユニットです。

14bit 300kspsの変換を最大で4チャネル同時に行うことができ、また、入力は

アナログデバイセズ社

のSSM2142/43による差動信号で受けます。

外部コネクタに直接装着します。コネクタ付近に見える基板の切り欠は、コネクタのラッチを引っかける個所です。

UnivIFのアナログフロントエンドとして開発したAD変換ユニットです。

14bit 300kspsの変換を最大で4チャネル同時に行うことができ、また、入力は

アナログデバイセズ社

のSSM2142/43による差動信号で受けます。

外部コネクタに直接装着します。コネクタ付近に見える基板の切り欠は、コネクタのラッチを引っかける個所です。

回路は、MAXIM社製シリアルA/D変換器 MAX121とSSM2143を4チャネルと、それらに電源を供給するDC-DCコンバータ、3端子レギュレータからなります。

接続用のコネクタは miniDIN 4ピンを使用していて、ビデオのS端子ケーブルがシールド線として流用できます。

このユニットをつかうと、A/D変換ボードとして使えることはもちろんのこと、変換した信号をディジタル処理、たとえば、フィルタによるノイズ除去や同期検波などを行うことが容易となります。

シリアルA/Dの煩わしさを隠蔽するために、PLD側でも、クロックと変換スタート信号を与えるのみでパラレル出力が得られる回路ブロックをつくってあります。

8CH 13bit DAユニット

おなじく、UnivIFのアナログフロントエンドとして開発したDA変換ユニットです。

13bit 8CHの出力ができ、1Msps程度で使用することができます。

出力は同じくSSM2142/43ペアの差動信号で伝送できるように設計しており、13bitの分解能を活かしたまま、多少離れた回路にもチャネル間の干渉なく、信号を伝えられます。

おなじく、UnivIFのアナログフロントエンドとして開発したDA変換ユニットです。

13bit 8CHの出力ができ、1Msps程度で使用することができます。

出力は同じくSSM2142/43ペアの差動信号で伝送できるように設計しており、13bitの分解能を活かしたまま、多少離れた回路にもチャネル間の干渉なく、信号を伝えられます。

回路は、MAXIM社製 D/Aコンバータ MAX574(PLCC)、基準電源MAX873?、ドライブ用のSSM2142、電源回路から成ります。

このDACは1個で6000円程度と気分的にはわりと高いICなのですが、13bitで1チャネルあたり700円くらいと思えば安いのかもしれません。

出力はおなじみRJ-45を使用していて、巷にあふれている100BASE-TX用のケーブルがそのまま流用できます(ちゃんとツイストペアも考慮してあります)。

しなみに、AD/DAユニットとも、左半分がでっぱった形になっていて、穴が開いていますが、この部分はちょうどサンハヤトのICB-93あたりと一致するようにつくってあったりします。

このユニットを使うと、アナログ信号の出力ができます(あたりまえ)。

以下のSRAMユニットを併用することで、DDS(Direct Digital Synthesizer)方式で高精度な正弦波信号や、AM変調、FM変調した信号を出力することができます。

また、特殊な例ではPLD内部のバス信号を直接DA出力することで、オシロスコープで内部の処理具合いを観測することができます。

256K高速SRAMユニット

PLDの基本要素、ロジックエレメント(LE)はラッチを含むため、データ等の記憶用にも使うことができます。

しかし、LEの数は限られており、記録を主にするには専用のメモリを使うべきです。

しかし、UnivIF Ver2では0、Ver3でも12Kbitしかメモリは内蔵されておらず、正弦波テーブルのような大きなものを作ったり、大容量のFIFOをつくろうとするとすぐに足りなくなります。

PLDの基本要素、ロジックエレメント(LE)はラッチを含むため、データ等の記憶用にも使うことができます。

しかし、LEの数は限られており、記録を主にするには専用のメモリを使うべきです。

しかし、UnivIF Ver2では0、Ver3でも12Kbitしかメモリは内蔵されておらず、正弦波テーブルのような大きなものを作ったり、大容量のFIFOをつくろうとするとすぐに足りなくなります。

そこで、拡張コネクタに高速SRAMをつけようと考えたのがこのユニット(写真左)です。

構造は、内部拡張コネクタ経由でPLDとSRAMを直結したものです。

PLD側は3.3V入出力、SRAMは5.0V品ですが、PLD側が3.3VでスイングするためRAMの入力はOK、一方PLD入力は5Vに耐性があるのでOKです。

SRAMは昔、Pentium時代に外部キャッシュとして多用されていたらしい、256Kbit(32Kbyte), 8bitバス幅, 15ns品です。

(実は、近くのジャンク屋で300円で売られていたマザーボードから6個取れたものです。普通に買おうとしたら入手性はあまり良くない上に1個数百円〜千数百円が50円なのでもうけもの(笑)、その後買い占めましたので当分困りません。)

PLD側にアクセス回路をつくって動作検証してみました。PLD側66MHz(サイクル15ns)で、2クロックでデータの読み出しor書き込み、3クロックで同一アドレスへの読み→書きができました。

最近の主な用途としては、あらかじめ正弦波のデータを書き込んでおいて、信号生成につかっています。

正弦波の1周期を65536(=2^16)として、対象性を考慮してその1/4(0-16383)を16bitで記録しています(16K*2=32Kbyteでぴったり)。

PLD側では、16bitで要求された位相を4象限に分類し、位相の反転、および符合の反転を行って16bit精度で出力して、次段の回路に渡すようにしました。

VCOユニット

UnivIFでは、APIC21の出力するクロック(33MHz/2=16.7MHz)がPLDに供給されています。

APIC21側のやりとりはこのクロックに同期させますが、デバイス自体はより高速のクロックにも耐えられます。

そのため、別途クロックを供給し、処理能力や時間分解能を向上させることを目的に、クロックコネクタが搭載されています。

UnivIFでは、APIC21の出力するクロック(33MHz/2=16.7MHz)がPLDに供給されています。

APIC21側のやりとりはこのクロックに同期させますが、デバイス自体はより高速のクロックにも耐えられます。

そのため、別途クロックを供給し、処理能力や時間分解能を向上させることを目的に、クロックコネクタが搭載されています。

VCOユニット(写真右)は、そのクロックコネクタに接続する可変周波数発振回路です。

PLD側から出力されるPWM信号に対して、そこそこ比例の単調増加の関係の周波数で発振します。

構造的には、PWMを受けてローパスフィルタでアナログ電圧に変換し、オペアンプとトランジスタによるボルテージフォロワ回路で、74VHC04(NB)の電源を駆動します。

74VHC04のインバータゲート奇数個をリングオッシレータとして使用し、PLDに返します。

また、制御電圧にトリマ抵抗でオフセットを与えて、PWMのデューティと発振周波数の関係をオフセットさせます。

PLDが3.3V駆動であり、閾値が1V台と低いため、レベル変換なしで動作しています。

リングオッシレータのインバータ数が5個で〜50MHz程度、3個で〜80MHz程度、1個で〜200MHz程度の発振が確認されています。

よく使用している66MHzの場合は3個リングにしています。

PLD側では、このVCOの出力を適宜分周したものと、APIC21からのクロックを分周したものをXORにかけ、その出力をVCOに戻します。

ロックがはずれた状態では、このPWM出力が平均的にデューティ50%となるため、そのときに目標の周波数近くで発振するようにVCOを調整すると、PLLがロックします。

現状では、あまり難しいことを考えずにカット&トライした回路であるため、ロックレンジもあまり広くなく、季節の代わり目(謎)にトリマの再調整が必要だったりしますが、それなりに便利です。

また、PLLの基準のおおもとはPCIのクロックですので、複数のUnivIFを使ったときに、ボード間でも同期がとれます。微妙な位相差はありますが、クロックの数のレベルで一致させたい用途では非常に便利です。

一方、同期が不要であれば、水晶発振器を直接使った方がクロック品質がよくなることは言うまでもありません。

|

| UnivIFフル装備 |

|

| 信号生成例 |

|

| モーションキャプチャ処理装置 |

以上のユニット類をフル装備で組み合わせた例を示します。

UnivIF+VCO+RAM+DAで、アナログ波形生成回路を構成しています。

あらかじめ、RAMに正弦波テーブルを書き込んでおき、それを読み出しながら、加工して出力します。

右の信号生成例ではバースト波に周波数変調(水色、上が低周波)と振幅変調(緑)をおこなっています(東北大学江村研で行われていた研究で使用した波形)。

下の写真は、研究中の磁気式モーションキャプチャの信号処理回路で、UnivIFV2+DAで6種類の正弦波の生成を行い、UnivIFV2+AD×2セットで4信号に対して6正弦波との同期検波を行っています(詳細は別ページで解説予定)。

UnivIFのアナログフロントエンドとして開発したAD変換ユニットです。

14bit 300kspsの変換を最大で4チャネル同時に行うことができ、また、入力は

アナログデバイセズ社

のSSM2142/43による差動信号で受けます。

外部コネクタに直接装着します。コネクタ付近に見える基板の切り欠は、コネクタのラッチを引っかける個所です。

UnivIFのアナログフロントエンドとして開発したAD変換ユニットです。

14bit 300kspsの変換を最大で4チャネル同時に行うことができ、また、入力は

アナログデバイセズ社

のSSM2142/43による差動信号で受けます。

外部コネクタに直接装着します。コネクタ付近に見える基板の切り欠は、コネクタのラッチを引っかける個所です。 おなじく、UnivIFのアナログフロントエンドとして開発したDA変換ユニットです。

13bit 8CHの出力ができ、1Msps程度で使用することができます。

出力は同じくSSM2142/43ペアの差動信号で伝送できるように設計しており、13bitの分解能を活かしたまま、多少離れた回路にもチャネル間の干渉なく、信号を伝えられます。

おなじく、UnivIFのアナログフロントエンドとして開発したDA変換ユニットです。

13bit 8CHの出力ができ、1Msps程度で使用することができます。

出力は同じくSSM2142/43ペアの差動信号で伝送できるように設計しており、13bitの分解能を活かしたまま、多少離れた回路にもチャネル間の干渉なく、信号を伝えられます。